# TECHNICAL INFORMATION SD-26

# **NMOS linear image sensors**

# HAMAMATSU

# Contents

| 2. Structure and basic operation       4         2-1. Structure       4         2-2. Charge integration method       4         2-3. Signal readout by shift register       5         3. Sensor types and operation       5         3. Current output type NMOS linear image sensors       6         3-2. Current output type NMOS linear image sensors       6         3-2. Contigurations       6         3-2.4. Readout method for the current output type       7         3-2.3. Readout method for the current output types       8         3-2.4. Terminal voitage for current output types       9         3-2.5. Input/output pulse timing for current output types       11         3-3. Voltage output type NMOS linear image sensors       12         3-3.4. Terminal voitage for current output types       12         3-3.4. Terminal voitage output types       13         3-3.4. Readout method for the voitage output types       13         3-3.4. Terminal voitage output types       14         3-3.5. Input/output characteristics       16         4-1.1. Input/output characteristics       16         4-1.1. Input/output characteristics       17         4.4. Photoresponse non-uniformity       18         4.5. Dark output       18         4.6. Resolution                                                                                                  | 1. Introduction                                         | 4 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---|

| 2-1. Structure       4         2-2. Charge integration method       4         2-3. Signal readout by shift register       5         3. Sensor types and operation       5         3. Sensor types of NMOS linear image sensors       5         3-2. Current output type NMOS linear image sensors       6         3-2.1. Configurations       6         3-2.2. Operating principle of current output type       7         3-2.3. Readout method for the current output types       8         3-2.4. Terminal voltage for current output types       9         3-2.5. Input/output puidse timing for current output types       11         3-3. Voltage output type NMOS linear image sensors       12         3-3.1. Configurations of the voltage output types       11         3-3. Voltage output type sensors       12         3-3.1. Configurations of the voltage output types       13         3-3.2. Operating principle of the voltage output types       13         3-3.3. Readout method for the voltage output types       13         3-3.4. Terminal voltage for the voltage output types       14         3-3.5. Input/output put sentiming for voltage output type       14         4. Characteristics       16         4-1.1. Input/output characteristics (voltage output type)       16         4-1.2. Input/v                                                       | 2. Structure and basic operation                        | 4 |

| 2-3. Signal readout by shift register       5         3. Sensor types and operation       5         3.1. Types of NMOS linear image sensors       5         3.2. Current output type NMOS linear image sensors       6         3.2.1. Configurations       6         3.2.2. Operating principle of current output types       7         3.2.3. Readout method for the current output types       8         3.2.4. Terminal voltage for current output types       9         3.2.5. Input/output pulse timing for current output types       11         3.3. Voltage output type NMOS linear image sensors       12         3.3.1. Configurations of the voltage output types       13         3.3.2. Operating principle of the voltage output types       13         3.3.3. Readout method for the voltage output types       13         3.3.3. Readout method for the voltage output types       14         3.3.4. Terminal voltage for the voltage output types       14         3.3.4. Input/output pulse timing for voltage output types       14         3.3.4. Input/output pulse timing for voltage output type       16         4.1. Input/output characteristics (current output type)       16         4.1. Input/output characteristics (voltage output type)       16         4.2. Linearity error       17         4.3. Spectral response characteris                    |                                                         |   |

| 3. Sensor types and operation       5         3-1. Types of NMOS linear image sensors       5         3-2. Current output type NMOS linear image sensors       6         3-2.1. Configurations       6         3-2.2. Operating principle of current output type       7         3-2.3. Readout method for the current output types       8         3-2.4. Terminal voltage for current output types       9         3-2.5. Input/output pulse timing for current output types       11         3-3. Voltage output type NMOS linear image sensors       12         3-3.1. Configurations of the voltage output types       13         3-3.2. Operating principle of the voltage output types       13         3-3.3. Readout method for the voltage output types       13         3-3.4. Terminal voltage for the voltage output types       13         3-3.5. Input/output characteristics       16         4.1. Input/output characteristics       16         4.1.1. Input/output characteristics (current output type)       16         4.1.2. Input/output characteristics (current output type)       16         4.1.2. Input/output characteristics (current output type)       16         4.1.2. Input/output characteristics (current output type)       16         4.1.3. Spectral response characteristics       17         4.4.4. Photoresponse non-uni                    | 2-2. Charge integration method                          |   |

| 3-1. Types of NMOS linear image sensors       5         3-2. Current output type NMOS linear image sensors       6         3-2-1. Configurations       6         3-2-2. Operating principle of current output type       7         3-2-3. Readout method for the current output types       8         3-2-4. Terminal voltage for current output types       9         3-2-5. Input/output publes timing for current output types       9         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       13         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output types       14         3-3-5. Input/output characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-1.1. Input/output characteristics (voltage output type)       16         4-1.2. Input/output characteristics (voltage output type) | 2-3. Signal readout by shift register                   |   |

| 3-1. Types of NMOS linear image sensors       5         3-2. Current output type NMOS linear image sensors       6         3-2-1. Configurations       6         3-2-2. Operating principle of current output type       7         3-2-3. Readout method for the current output types       8         3-2-4. Terminal voltage for current output types       9         3-2-5. Input/output publes timing for current output types       9         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       13         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output types       14         3-3-5. Input/output characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-1.1. Input/output characteristics (voltage output type)       16         4-1.2. Input/output characteristics (voltage output type) | 3. Sensor types and operation                           | 5 |

| 3-2. Current output type NMOS linear image sensors       6         3-2.1. Configurations       6         3-2.2. Operating principle of current output types       7         3-2.3. Readout method for the current output types       8         3-2.4. Terminal voltage for current output types       9         3-2.5. Input/output pulse timing for current output type       11         3-3. Voltage output type NMOS linear image sensors       12         3-3.1. Configurations of the voltage output types       13         3-3.2. Operating principle of the voltage output types       13         3-3.3. Readout method for the voltage output types       13         3-3.4. Terminal voltage output types       14         3-3.5. Input/output pulse timing for voltage output types       14         3-3.5. Input/output pulse timing for voltage output type       14         3-3.5. Input/output characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-2. Linearity error       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4.5. Dark output       18         4.6. Resolution       20         4.7. Lag       21         4.8. Noise       22                                                                                              |                                                         |   |

| 3-2-2. Operating principle of current output types       7         3-2-3. Readout method for the current output types       8         3-2-4. Terminal voltage for current output types       9         3-2-5. Input/output pulse timing for current output type       11         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage output types       13         3-3-5. Input/output pulse timing for voltage output types       14         3-3-6. Configurations of the voltage output types       14         3-3-7. Readout method for the voltage output types       14         3-3-8. Input/output pulse timing for voltage output types       14         4. Characteristics       16         4-1-1. Input/output characteristics (current output type)       16         4-2. Linearity error       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4-5. Dark output       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       23         4-9. Shift register frequency characteristics                                                                       |                                                         |   |

| 3-2-3. Readout method for the current output types       8         3-2-4. Terminal voltage for current output type       9         3-2-5. Input/output pulse timing for current output type       11         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       13         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output types       14         3-3-6. Linput/output characteristics       16         4-1. Input/output characteristics (current output type)       16         4-1.1. Input/output characteristics (voltage output type)       16         4-1.2. Linearity error.       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4.7. Lag       21         4.8. Noise       22         4.8.1. Random noise in current output type)       23         4.9. Shift register frequency characteristics       24         4.10. Characteristic change by UV exposure       25                                                                | 3-2-1. Configurations                                   |   |

| 3-2-4. Terminal voltage for current output types       9         3-2-5. Input/output pulse timing for current output type       11         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       13         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output types       14         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output types       14         4. Characteristics       16         4-1. Input/output characteristics (current output type)       16         4-1-2. Input/output characteristics (current output type)       16         4-1-2. Input/output characteristics       17         4-3. Spectral response characteristics       17         4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8. 1. Random noise in current output type       23         4-9. Shift register frequency characteristics                                                            |                                                         |   |

| 3-2-5. Input/output pulse timing for current output type       11         3-3. Voltage output type NMOS linear image sensors       12         3-3-1. Configurations of the voltage output types       12         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4-3. Spectral response characteristics       17         4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Random noise in current output type       22         4-8.2. Random noise in current output type       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by U                                                       |                                                         |   |

| 3-3. Voltage output type NMOS linear image sensors       12         3-3.1. Configurations of the voltage output types       12         3-3-2. Operating principle of the voltage output types       13         3-3.3. Readout method for the voltage output types       13         3-3.3. Readout method for the voltage output types       13         3-3.4. Terminal voltage for the voltage output types       14         3-3.5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26 <td></td> <td></td>                                                                                   |                                                         |   |

| 3-3-1. Configurations of the voltage output types       12         3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4.1. Input/output characteristics       16         4.1. Input/output characteristics (current output type)       16         4.1.2. Input/output characteristics (voltage output type)       16         4.2. Linearity error       17         4.3.3.5. Dark output       18         4-5. Dark output       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       22         4-8.2. Random noise in current output type       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26         5-3. Light sources       <                                                                                                                                  |                                                         |   |

| 3-3-2. Operating principle of the voltage output types       13         3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1-2. Input/output characteristics (current output type)       16         4-1-2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4-3. Spectral response characteristics       17         4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26         5-3. Light sources       27                                                                                                                             |                                                         |   |

| 3-3-3. Readout method for the voltage output types       13         3-3-4. Terminal voltage for the voltage output types       14         3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4-1. Input/output characteristics (current output type)       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (current output type)       16         4-2. Linearity error       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       23         4-9. Shift register frequency characteristics       23         4-9. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26         5-3. Light sources       27         5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                           |                                                         |   |

| 3-3-4. Terminal voltage for the voltage output type       14         3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4.1. Input/output characteristics       16         4-1-1. Input/output characteristics (current output type)       16         4-1-2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4-3. Spectral response characteristics       17         4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8-1. Random noise in current output type       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-2. Output estimation       26         5-3. Light sources       27         5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                                                                                                                                                                    |                                                         |   |

| 3-3-5. Input/output pulse timing for voltage output type       14         4. Characteristics       16         4-1. Input/output characteristics       16         4-1.1. Input/output characteristics (current output type)       16         4-1.2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4.3. Spectral response characteristics       17         4.4. Photoresponse non-uniformity       18         4.5. Dark output       18         4.6. Resolution       20         4.7. Lag       21         4.8. Noise       22         4.8. Noise       22         4.8.1. Random noise in current output type       23         4.9. Shift register frequency characteristics       24         4.10. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26         5-3. Light sources       27         5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                                                                                                                                                              |                                                         |   |

| 4. Characteristics       16         4-1. Input/output characteristics (current output type)       16         4-1-1. Input/output characteristics (voltage output type)       16         4-1-2. Input/output characteristics (voltage output type)       16         4-2. Linearity error       17         4-3. Spectral response characteristics       17         4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8-1. Random noise in current output type)       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-2. Output estimation       26         5-3. Light sources       27         5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                         |   |

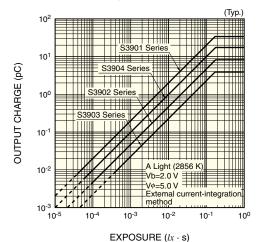

| 4-1. Input/output characteristics164-1-1. Input/output characteristics (current output type)164-1-2. Input/output characteristics (voltage output type)164-2. Linearity error174-3. Spectral response characteristics174-4. Photoresponse non-uniformity184-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |   |

| 4-1-1. Input/output characteristics (current output type)164-1-2. Input/output characteristics (voltage output type)164-2. Linearity error174-3. Spectral response characteristics174-4. Photoresponse non-uniformity184-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-2. Output estimation265-3. Light sources275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                         |   |

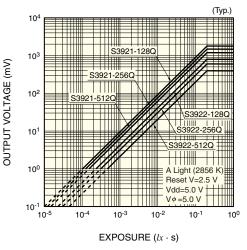

| 4-1-2. Input/output characteristics (voltage output type)164-2. Linearity error174-3. Spectral response characteristics174-4. Photoresponse non-uniformity184-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type224-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |   |

| 4-2. Linearity error174-3. Spectral response characteristics174-4. Photoresponse non-uniformity184-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type224-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |   |

| 4-3. Spectral response characteristics174-4. Photoresponse non-uniformity184-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8.1. Random noise in current output type224-8.2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |   |

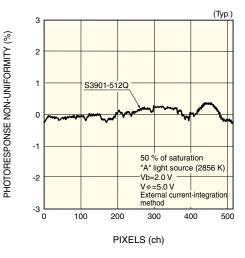

| 4-4. Photoresponse non-uniformity       18         4-5. Dark output       18         4-6. Resolution       20         4-7. Lag       21         4-8. Noise       22         4-8.1. Random noise in current output type       22         4-8-2. Random noise (voltage output type)       23         4-9. Shift register frequency characteristics       24         4-10. Characteristic change by UV exposure       25         5. Precautions       26         5-1. Integration time setting       26         5-2. Output estimation       26         5-3. Light sources       27         5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                       |   |

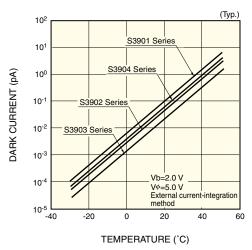

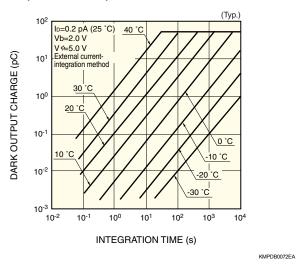

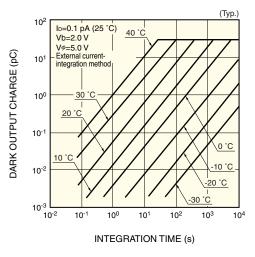

| 4-5. Dark output184-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type224-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |   |

| 4-6. Resolution204-7. Lag214-8. Noise224-8-1. Random noise in current output type224-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |   |

| 4-7. Lag214-8. Noise224-8. Noise224-8.1. Random noise in current output type224-8.2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                       |   |

| 4-8. Noise224-8.1. Random noise in current output type224-8-1. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         |   |

| 4-8-1. Random noise in current output type224-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                       |   |

| 4-8-2. Random noise (voltage output type)234-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                         |   |

| 4-9. Shift register frequency characteristics244-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |   |

| 4-10. Characteristic change by UV exposure255. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |   |

| 5. Precautions265-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |   |

| 5-1. Integration time setting265-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |   |

| 5-2. Output estimation265-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |   |

| 5-3. Light sources275-4. Positional accuracy of photosensitive area275-5. Precautions during handling28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |   |

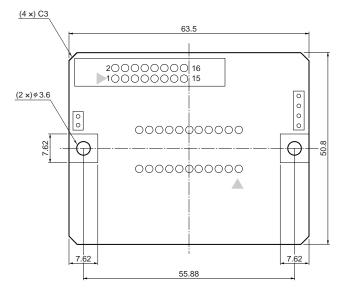

| 5-4. Positional accuracy of photosensitive area       27         5-5. Precautions during handling       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |   |

| 5-5. Precautions during handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |   |

| 5-6. Precautions when configuring driver circuit boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-6. Precautions when configuring driver circuit boards |   |

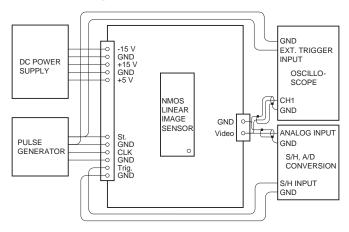

| 6. Recommended driver circuits                                                         |    |

|----------------------------------------------------------------------------------------|----|

| 6-1-1. Current-to-voltage conversion method                                            |    |

| 6-1-2. External current-integration method                                             |    |

| 6-2. Driver circuit for voltage output type image sensor                               |    |

| 6-3. Pulse generator                                                                   | 44 |

| 7. Standard driver circuits                                                            |    |

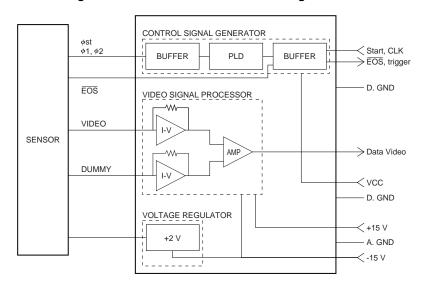

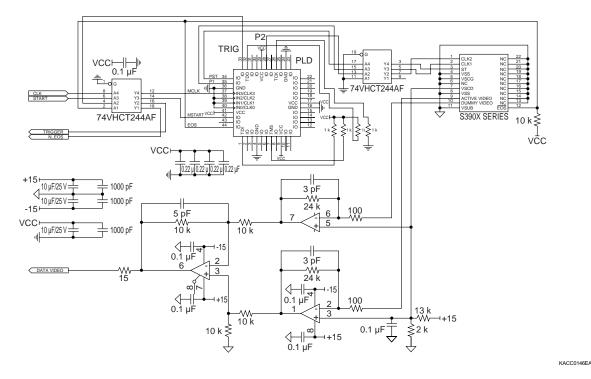

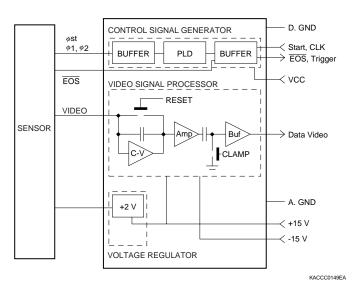

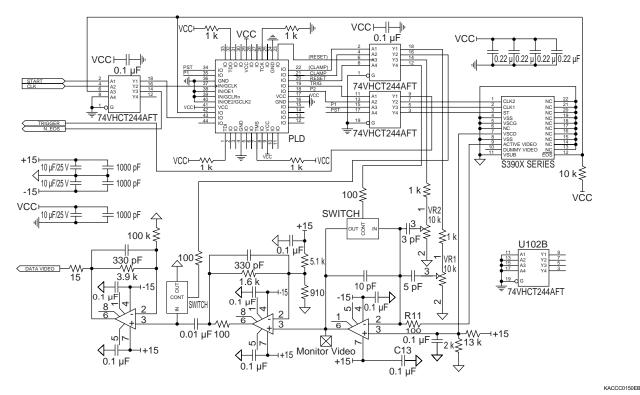

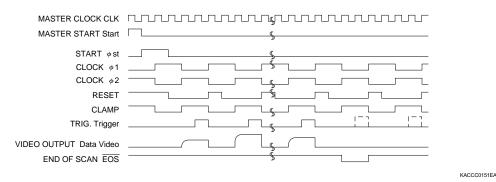

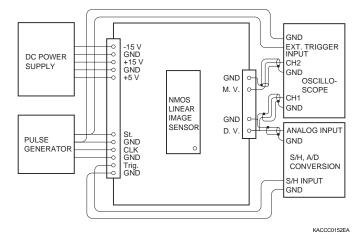

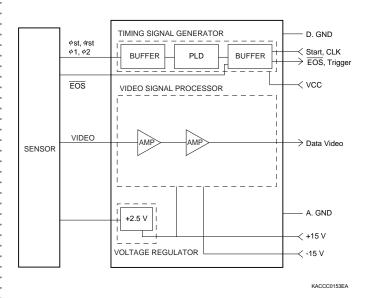

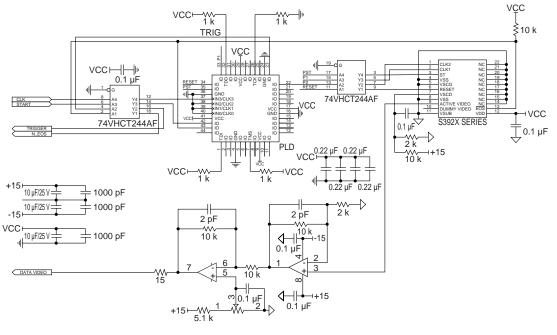

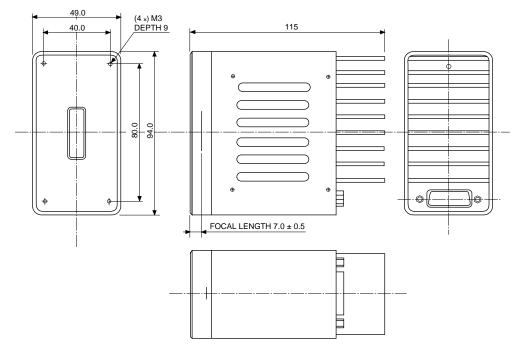

| 7-1. Driver circuit configurations                                                     | 45 |

| 7-2. Driver circuit functions                                                          | 45 |

| 7-3. External current-integration circuit C7884 series for current-output image sensor | 47 |

| 7-3-1. Product lineup                                                                  | 47 |

| 7-3-2. Specifications                                                                  | 47 |

| 7-3-3. How C7884 series differs from recommended circuit                               | 48 |

| 8. Reliability                                                                         | 49 |

# 1. Introduction

The NMOS linear image sensor is a self-scanning photodiode array designed specifically for detectors used in multichannel spectroscopy. The NMOS linear image sensor offers a number of features, for example, a large photosensitive area, high UV sensitivity, stable performance against UV exposure, wide dynamic range due to low dark current and high saturation charge, superior output linearity and uniformity, and also low power consumption. In addition to standard types with a quartz window, devices with a fiber optic plate are available allowing efficient optical coupling to other imaging devices. Applications include not only spectroscopy but also a diverse range of image readout systems.

# 2. Structure and basic operation

This section explains the structure and operations of NMOS linear image sensors.

# 2-1. Structure

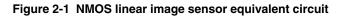

An NMOS linear image sensor, as shown in Figure 2-1, consists of a photosensitive section constructed with a photodiode array, a switch section that reads out the signal from the photodiode array, and a shift register that addresses these switches.

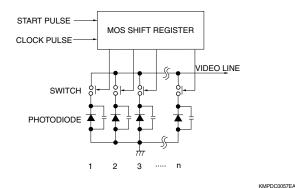

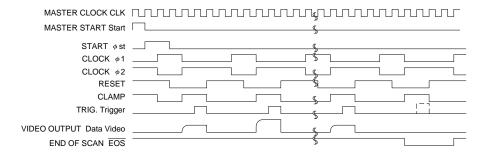

In contrast to the real-time signal readout method used for most photodiodes, the NMOS linear image sensor uses a charge integration method to read out the signal. In this method, an electrical charge generated by photoelectric conversion at the photodiode array is temporarily stored in the junction capacitance of each photodiode. The signal stored in each photodiode is read out through an output line (video line) by sequentially turning on the address switch connected to each photodiode at a delayed timing with respect to the preceding signal. The MOS shift register is used to produce the address pulses that turn on these switches. A typical output timing diagram is shown in Figure 2-2.

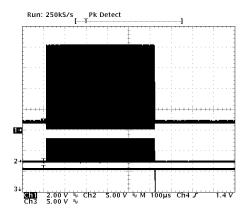

#### Figure 2-2 Output timing diagram

# 2-2. Charge integration method

In the real-time readout method used for most photodiodes, the signal output is proportional only to the incident light intensity. In the charge integration method, however, the signal output is obtained in proportion to the product of light intensity and integration time, that is, the signal output is proportional to the amount of light exposure. This means that the signal output level can be increased by making the integration time longer, enabling low-light-level detection even with a photodiode with small photosensitive area.

In NMOS linear image sensor operation, the integration time of each photodiode is the time interval between when one switch is turned on for signal readout, and the time at which the same switch is turned on for the next readout. This is equal to the time interval between each start pulse signal for the MOS shift register. If the incident light level changes within this integration time, the change cannot be read out. Strictly speaking, the start time for integration does shift slightly because the switch for each photodiode is time-sequentially turned on as the signal is read out. Therefore, if the light level varies with time, the signal output from each photodiode does not become constant even though the entire image sensor is uniformly illuminated.

There is an upper limit on the output charge since the junction capacitance in which a signal charge is stored is finite. This is called the saturation charge above which the signal output will not increase with excessive light.

# 2-3. Signal readout by shift register

As stated above, NMOS linear image sensors use the charge integration method in which the signal from each photodiode is time-sequentially read out through one output line. It is not therefore necessary to connect an individual readout circuit to each photodiode. This means the external circuit configuration is made simple.

When an external start pulse is applied to the shift register while a two-phase clock pulse is being input, an address pulse is sequentially sent to turn on the address switch of the 1st channel photodiode and thus the signal stored in each photodiode is read out. If the next start pulse is introduced to the shift register before the signals of all channels are read out, then two address switches turn on at the same time, resulting in erroneous operation. Accordingly, the start pulse interval (integration time) must be set longer than the readout time required for all channels.

NMOS linear image sensors use a different readout method than for normal photodiodes. It is essential that the user understand these distinctions to make optimum settings to match operating conditions such as incident light level and integration time length.

# 3. Sensor types and operation

This section explains the types and configurations of Hamamatsu NMOS linear image sensors as well as their operating principles.

### 3-1. Types of NMOS linear image sensors

Hamamatsu NMOS linear image sensors are available in the following two readout methods.

- 1. Current output type S3901 to S3904 series, etc.

- 2. Voltage output type S3921 to S3924 series

The current output type offers superior linearity when used with an external signal readout circuit operating in the current integration mode, making it ideally suited for use in applications where high accuracy is particularly needed. The current output type also gives a high-speed readout when used with the current-to-voltage conversion method.

The voltage output type NMOS linear image sensors use the same output section as the current output type, but further in-

Table 3-1

Quick reference for Hamamatsu NMOS linear image sensors

#### Current output type

| Type No.       | Number of pixels | Pixel size<br>(pixel pitch × height)<br>(μm) | Active area<br>[mm (H) × mm (V)] | Feature                                                                      |  |  |

|----------------|------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------|--|--|

| S3901-128Q     | 128              |                                              | 6.4 × 2.5                        |                                                                              |  |  |

| S3901-256Q, F  | 256              | 50 × 2500                                    | 12.8 × 2.5                       |                                                                              |  |  |

| S3901-512Q, F  | 512              |                                              | 25.6 × 2.5                       |                                                                              |  |  |

| S3904-256Q     | 256              |                                              | 6.4 × 2.5                        |                                                                              |  |  |

| S3904-512Q, F  | 512              | 25 × 2500                                    | 12.8 × 2.5                       |                                                                              |  |  |

| S3904-1024Q, F | 1024             |                                              | 25.6 × 2.5                       | <ul> <li>Low power consumption</li> <li>Superior output linearity</li> </ul> |  |  |

| S3902-128Q     | 128              |                                              | 6.4 × 0.5                        | Wide dynamic range                                                           |  |  |

| S3902-256Q     | 256              | 50 × 500                                     | 12.8 × 0.5                       |                                                                              |  |  |

| S3902-512Q     | 512              |                                              | 25.6 × 0.5                       |                                                                              |  |  |

| S3903-256Q     | 256              |                                              | 6.4 × 0.5                        |                                                                              |  |  |

| S3903-512Q     | 512              | 25 × 500                                     | 12.8 × 0.5                       |                                                                              |  |  |

| S3903-1024Q    | 1024             |                                              | 25.6 × 0.5                       |                                                                              |  |  |

#### Voltage output type

| Type No.      | Number of pixels | Pixel size<br>(pixel pitch × height)<br>(μm) | Active area<br>[mm (H) × mm (V)] | Feature                   |  |  |

|---------------|------------------|----------------------------------------------|----------------------------------|---------------------------|--|--|

| S3921-128Q    | 128              |                                              | 6.4 × 2.5                        |                           |  |  |

| S3921-256Q    | 256              | 50 × 2500                                    | 12.8 × 2.5                       |                           |  |  |

| S3921-512Q, F | 512              |                                              | 25.6 × 2.5                       |                           |  |  |

| S3924-256Q    | 256              |                                              | 6.4 × 2.5                        |                           |  |  |

| S3924-512Q, F | 512              | 25 × 2500                                    | 12.8 × 2.5                       | Boxcar output waveform    |  |  |

| S3924-1024Q   | 1024             |                                              | 25.6 × 2.5                       | • Simple external readout |  |  |

| S3922-128Q    | 128              |                                              | 6.4 × 0.5                        | circuit                   |  |  |

| S3922-256Q    | 256              | 50 × 500                                     | 12.8 × 0.5                       | Wide dynamic range        |  |  |

| S3922-512Q    | 512              |                                              | 25.6 × 0.5                       |                           |  |  |

| S3923-256Q    | 256              |                                              | 6.4 × 0.5                        |                           |  |  |

| S3923-512Q    | 512              | 25 × 500                                     | 12.8 × 0.5                       |                           |  |  |

| S3923-1024Q   | 1024             |                                              | 25.6 × 0.5                       |                           |  |  |

clude a signal processing circuit that consists of a current integration circuit utilizing video line capacitance and an impedance conversion circuit. Although the linearity accuracy is slightly lower than the current output type operated in the current integration mode, the voltage output type can internally produce a low-impedance output signal with boxcar waveform. This allows signal readout with a simple external circuit.

Table 3-1 gives the major product line of Hamamatsu NMOS linear image sensors. Suffix "Q" of the type number means the image sensors have a quartz window, while suffix "F" indicates a fiber optic plate is used. The quartz window types ensure high sensitivity in the UV range and also provide stable operation for dark current and sensitivity performance even after extended periods of UV exposure. Image sensors having a fiber optic plate can be easily fiber-coupled to another optical element such as an image intensifier. For detection of X-rays from 10 keV to 100 keV, semi-custom devices ("FX" type) having a phosphor-coated fiber optic plate are also available in each family of current output and voltage output type NMOS linear image sensors. Furthermore, S8380/S8381 series devices with enhanced near infrared sensitivity are provided.

# 3-2. Current output type NMOS linear image sensors

#### 3-2-1. Configurations

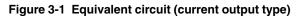

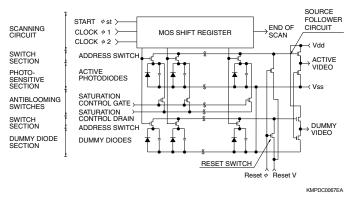

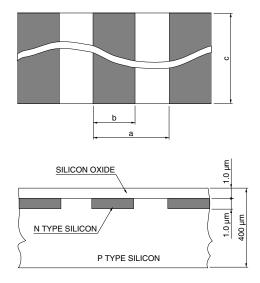

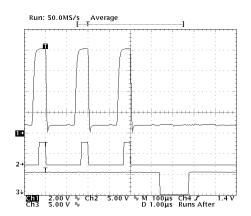

The current output type NMOS linear image sensor consists of a photosensitive section, readout switch section and shift register, integrated into a single chip. In addition, dummy photodiodes and anti-blooming switches are formed on the same chip. Figure 3-1 shows the equivalent circuit for the current output type and Figure 3-2 shows the pinout configurations. The pin designations and their functions are listed in Table 3-2.

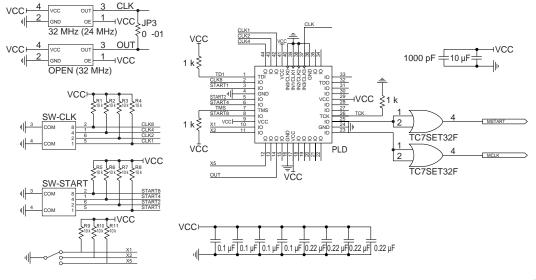

#### Figure 3-2 Pinout (current output type)

ACT

DUN

|              | •  |    |             |

|--------------|----|----|-------------|

| ¢2 🗌         | 1  | 22 |             |

| ¢1 🗌         | 2  | 21 |             |

| øst [        | 3  | 20 |             |

| Vss 🗌        | 4  | 19 |             |

| Vscg         | 5  | 18 |             |

| NC 🗌         | 6  | 17 |             |

| Vscd         | 7  | 16 |             |

| Vss 🗌        | 8  | 15 |             |

| FIVE VIDEO 🗌 | 9  | 14 |             |

| MMY VIDEO 🗌  | 10 | 13 |             |

| Vsub         | 11 | 12 | END OF SCAN |

|              |    |    |             |

|              |    |    |             |

KMPDC0021EA

Table 3-2 Pin description (current output type)

|        | Terminal     | Function                 |  |  |

|--------|--------------|--------------------------|--|--|

|        | φ1           | Clock pulse 1            |  |  |

|        | φ2           | Clock pulse 2            |  |  |

| Input  | φ <b>s</b> t | Start pulse              |  |  |

|        | Vscd         | Saturation control drain |  |  |

|        | Vscg         | Saturation control gate  |  |  |

|        | Vss          | Ground (anode potential) |  |  |

| Ground | Vsub         | Substrate potential      |  |  |

|        | NC           | No connection            |  |  |

|        | Active video | Signal output            |  |  |

| Output | Dummy video  | Switching noise output   |  |  |

|        | EOS          | End of scan              |  |  |

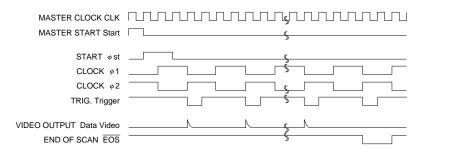

#### 1) Shift register

The shift register is comprised of N-channel MOS transistors. Pins  $\phi 1$ ,  $\phi 2$  and  $\phi st$  in Figure 3-2 are input pulse terminals used to operate the shift register. When an external start pulse  $\phi st$  is supplied to the shift register with the two-phase clock pulse  $\phi 1$  and  $\phi 2$  being applied, the shift register begins operation and generates a train of address pulses to sequentially turn on the address switch beginning with the 1st channel. The shift register is designed for low power consumption to minimize temperature rise in the sensor elements. When one scan for all pixels is completed, an end-of-scan (EOS) pulse is output at a timing immediately after the last pixel is readout.

#### (2) Photosensitive section

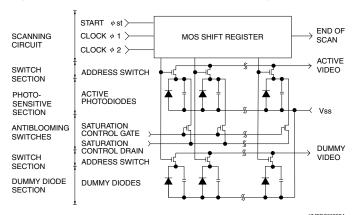

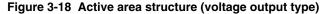

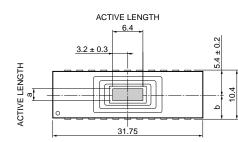

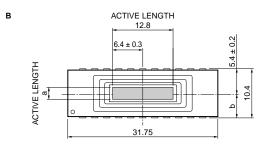

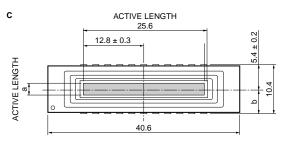

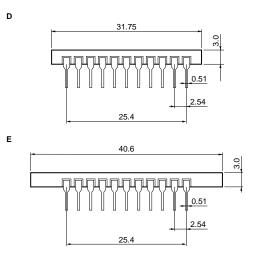

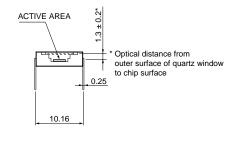

The photosensitive section is constructed with P-N junction photodiodes consisting of an N-type diffusion layer formed on a P-type silicon substrate. This section serves as a photoelectric converter that transforms light signals into electrical signals, and also temporarily stores the signal charge obtained. Pin Vss is connected to the anode (P-type silicon) of each photodiode. The photodiode is designed and processed to provide high UV sensitivity yet low dark current. The structure of the photosensitive section is shown in Figure 3-3, in which "a" is the photodiode pitch, "b" is the width of the photodiode diffusion layer and "c" is the photodiode height.

Figure 3-3 Active area structure (current output type)

#### (3) Dummy photodiode

Dummy photodiodes generate a spike noise signal used for external cancellation of spike noise in the current-to-voltage conversion readout method. These photodiodes are shielded with aluminum so that they are impervious to light.

#### (4) Readout switch

The readout switch section consists of an address switch array made up of N-channel MOS transistors, with the source of each transistor connected to the cathode of a photodiode or dummy photodiode while the drain and gate are connected respectively, to the video line and address pulse input. Each photodiode in the photosensitive section is connected to the video line via the individual address switch. When an address pulse is applied from the shift register, the two address switches turn on at the same time, and the output signal including spike noise is derived from the active video line, while the spike noise signal is output from the dummy video line. When the image sensor is operated in the current-to-voltage conversion method, the output signal can be obtained with low spike noise, by performing external differential amplification of each signal from the two video lines. The spike noise appears via floating capacitance between the gate and drain of each address switch at the time that the address pulse is introduced.

#### (5) Anti-blooming switch

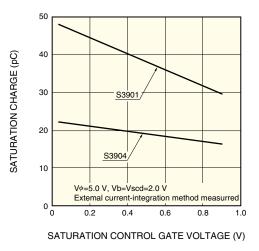

The anti-blooming switch section comprises a switch array constructed with N-channel MOS transistors, with the source of each transistor connected to the cathode of a photodiode while the drain and gate are connected respectively, to the saturation control drain Vscd and saturation control gate Vscg.

When a light higher than the saturation exposure enters a pho-

todiode, the photodiode cannot store a signal charge in excess of the saturation charge. Without saturation control, this causes the excess signal charge to overflow and diffuse into the adjacent photodiodes and the video line, resulting in deterioration of signal purity, so-called "blooming".

An anti-blooming switch is provided in Hamamatsu NMOS linear image sensors for each photodiode separately from the normal signal output line connected to the video line, in order to allow the excess charge to bleed off.

#### 3-2-2. Operating principle of current output type

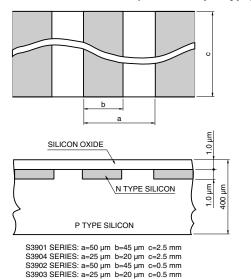

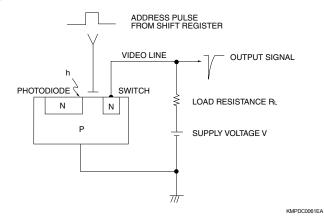

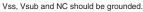

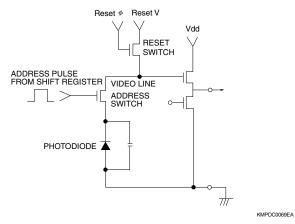

Figure 3-4 shows the structure of one pixel comprised of a photodiode and a readout switch, and Figure 3-5 shows its equivalent circuit. Specific operations are described below.

#### Figure 3-4 Readout section structure

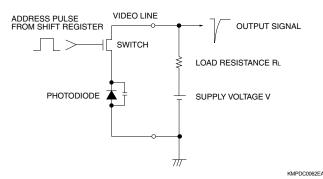

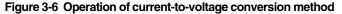

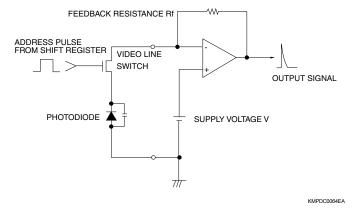

#### Figure 3-5 Equivalent circuit of current-to-voltage conversion method

The photodiode is a P-N junction photodiode consisting of an N-type diffusion area formed on a P-type silicon substrate. The readout switch consists of an N-channel MOS transistor, with its source connected to the cathode of a photodiode while the drain and gate are respectively connected to the video line and the address pulse input part from the shift register. The photodiode anode (silicon substrate) is connected to GND, and the video line is biased at the positive potential Vb.

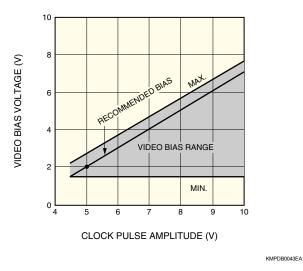

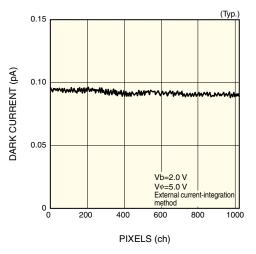

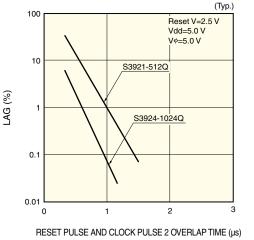

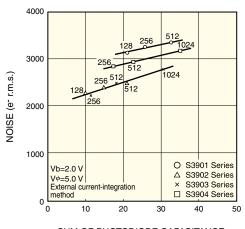

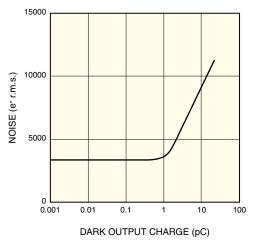

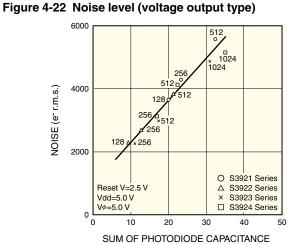

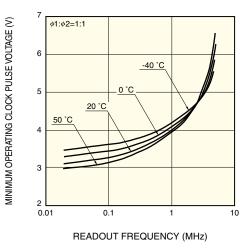

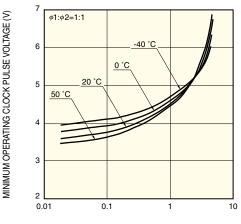

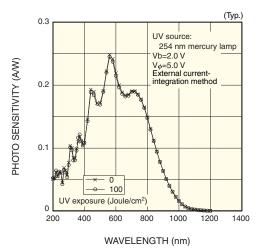

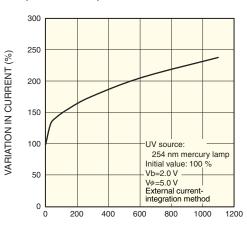

When an address pulse from the shift register is input to the gate of the readout switch, the switch turns on. As a result, the photodiode cathode sets to the same potential as that of the video line and the photodiode is initialized and reverse-biased. Thus the photodiode junction capacitance Cj is fed with a charge, Qj=Cj